产品详情

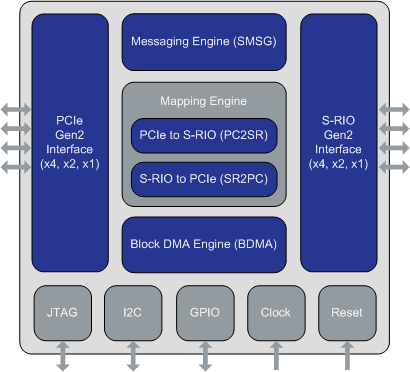

- x4 PCIe V2.1 to x4 S-RIO V2.1

- Single port: x4, x2 or x1 支持

- 1.25, 2.5, 3.125 and 5 Gbaud 支持

- Multiple DMA and Messaging channels/engines each capable of 支持ing full 20 Gbaud I/O

- 8Kbyte packet buffering per DMA and Messaging Channel

- 20 Baud line rate performance for 64 byte or larger packets, max TLP payload 256 bytes, max block DMA 64 Mbyte

- PCI Express non-transparent bridging for trans行动 mapping

- Lane reversal

- Automatic Polarity inversion for PCI Express

- Typical power 2W

- Reach 支持: 60 cm over 2 connectors

- 100, 125, 156.25 MHz S-RIO and PCIe Endpoint compatible clocking options

- JTAG 1149.1 and 1149.6

- 13x13 mm FCBGA

- 工业的 and Commercial options

The Tsi721 converts from PCIe to RapidIO and vice versa and provides full line rate bridging at 20 Gbaud. Using the Tsi721 designers can develop heterogeneous systems that leverage the peer to peer networking performance of RapidIO while at the same time using multiprocessor clusters that may only be PCIe enabled. Using the Tsi721, 应用s that require large amounts of data transferred efficiently without processor involvement can be executed using the full line rate block DMA+Messaging engines of the Tsi721.

产品文档

类型

姓名

日期

动作

2025-08-25

Tsi721 Product Brief

2025-08-25

RapidIO2 Switch 概览 Portfolio

2025-08-25

S-RIO Switch Feature Comparison Chart

2025-08-25

PCIe2 to S-RIO2 Bridging and Switching Evaluation Platform Quick Start Guide

2025-08-25

Tsi721 BSDL Model

2025-08-25

Tsi721 IBIS Model - 2.5V

2025-08-25

Tsi721 数据表

2025-08-25

Tsi721 User Manual

2025-08-25

PCIe2 to S-RIO2 Bridging and Switching Evaluation Platform Manual

2025-08-25

PCIe2 to S-RIO2 Bridging and Switching Evaluation Platform Schematic

2025-08-25

Tsi721 Thermal Compact Model (Fl其他m) FCBGA Detailed

2025-08-25

Tsi721 Thermal Compact Model (Fl其他m) FCBGA 2R

2025-08-25

S-RIO Linux 支持

2025-08-25

Tsi721 IBIS Model - 3.3V

2025-08-25

Supercomputing at the Mobile Edge 概览

2025-08-25

PDN#: F-16-01 PRODUCT DISCONTINUANCE NOTICE FOR 选择 DEVICES

2025-08-25

PCN# : A1706-01 Change in Bumping 地点 on 选择 包裹s

Boards and Kits

PCIe2 to S-RIO2 Evaluation Board

The IDT Tsi721-16GEBI Evaluation Board is a prototyping platform that leverage’s IDT’s Tsi721 PCIe® to RapidIO® Gen2 bridge as well as the CPS-1432 RapidIO Gen2 switch, allowing any PCIe processor to communicate to an S-RIO network. The Tsi721-16GEBI Evaluation board has a variety of interfaces that allows customers to interface DSPs, Microprocessors, and FPGAs to IDT 开关, and also allows for x86 processors to interface to an S- RIO network through the Tsi721 bridge. Interfaces include AMCs, SMAs, InfiniBand/CX4 and SFP+ connectors. This allows customers to implement most network configurations that represent their production hardware in a logically equivalent manner. By doing so, systems firmware and software engineers can start implementing their code before production hardware is available thereby accelerating development cycles and time to market.

The Tsi721-16GEBI evaluation board can network together multiple processors in individual PCs. Each PC is populated with a Tsi721 evaluation board. Each evaluation board is networked together over S-RIO, allowing for a cluster of PCIe enabled x86 processors over S-RIO.

The Tsi721-16GEBI evaluation board comes equipped with RapidFET JTAG, a software tool that can configure IDT 开关 and bridges out of band via the JTAG interface on the board, making access to registers simple via a user friendly Graphical User Interface.

您还有其他问题吗?

我们致力于帮助您探索各种可能性,优化性能,并推动技术进步。立即联系我们!

与销售人员交谈